1<sup>st</sup> Asia-Pacific Conference on Plasma Physics, 18-23, 09.2017, Chengdu, China

## System-on-Chip (SoC) Technology for Tokamak Electron Cyclotron Emission Imaging and Microwave Imaging Reflectometry

Y. Zhu<sup>1</sup>, Y. Wang<sup>1</sup>, B. Tobias<sup>2</sup>, C. Luo<sup>1</sup>, J.-H. Yu<sup>1</sup>, A.-V. Pham<sup>1</sup>, C.W. Domier<sup>1</sup>, A. Diallo<sup>3</sup>, G.J. Kramer<sup>3</sup>, Y. Ren<sup>3</sup>, R. Nazikian<sup>3</sup>, and N.C. Luhmann, Jr.<sup>1</sup>,

<sup>1</sup>University of California at Davis, USA, <sup>2</sup>Los Alamos National Laboratory, USA, <sup>3</sup>Princeton Plasma Physics Laboratory, USA

The importance of Microwave imaging instruments for diagnosis of electron temperature fluctuations (electron cyclotron emission imaging-ECEI) and electron density fluctuations (microwave imaging reflectometry-MIR) is attested to by their implementation on a number of tokamaks including ASDEX-Upgrade, DIII-D, EAST, J-TEXT, and KSTAR where they have facilitated diverse physics studies including Alfvén eigenmodes, ELM suppression and disruptions, and sawtooth reconnection<sup>1-5</sup>. We may now report on two major technological improvements:

1- By adding a V-Band (50 – 75 GHz) MMIC LNA (gain ~ 15 dB and noise temperature ~ 500 K) before the mixer diode, the overall noise temperature is reduced from as much as 250,000 K to as little as 2,000 K<sup>6</sup>.

2- A new system-on-chip (SoC) approach is capable of not only incorporating improvement in system noise temperature, but also provides a) shielding against interference from RF heating and strong bursts of mmwave radiation that sometimes originate in the plasma, and b) the ability to amplify and multiply low-frequency sources to generate high-frequency LO signals directly on the individual chips.

Improved noise temperature facilitates absolute temperature calibration, which is of vital importance for obtaining electron temperature profiles. Another important benefit pertains to the MIR systems, where preamplification significantly lowers the LO power requirement for each channel. This permits an increased number of channels for wider plasma coverage. Shielding against interference provides better data in more challenging experiments. And on-chip LO multiplication eliminates the need for bulky and expensive LO waveguide and LO optics.

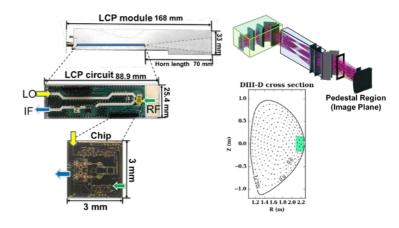

First, commercially available GaAs MMICs including the low-noise pre-amplifier, mixer, LO multiplier chain, and IF amplifier were combined on a liquid crystal polymer (LCP) substrate as a proof-of-principle demonstration in the upper V-Band (60-75 GHz)<sup>7</sup>.

Next, a compact "system-on-chip" (SoC) approach was undertaken where complete GaAs chip receivers including mm-wave LNA, balanced mixer, x6 LO multiplier chain, and microwave IF amplifier are mounted in waveguide horn antenna enclosures and stacked to form an array within a shielded enclosure<sup>8</sup>. This technology is being installed as a new imaging instrument on DIII-D. For the initial tests, it will take the place of the current low field side ECEI array. Minor modifications of the optics allow the new antennas to preserve the imaging performance.

Upon demonstrating improved noise temperature and shielding, the new instrument will be used to diagnose edge-localized modes and fluctuations of the high-confinement, or H-mode, pedestal. This has never before been achieved for the most ITER-relevant, low-collisionality regimes found on DIII-D, where transient bursts of radiation have limited past investigations.

## Acknowledgments

This work is supported by US DoE grants DE-AC02-09CH11466 and DE-FG02-99ER54531.

## References

- (1) H.K. Park, et al., Phys. Rev. Lett. 96, 195003 (2006)

- (2) H.K. Park, et al., Phys. Rev. Lett. 96, 195006 (2006)

- (3) I.G.J. Classen, et al., Phys. Rev. Lett. **98**, 035001 (2007)

- (4) B.J. Tobias, et al., Phys. Rev. Lett. **106**, 075003 (2011)

- (5) G.S. Yun, et al., Phys. Rev. Lett. 107 045004 (2011)

- (6) J. Lai, et al., Rev. Sci. Instrum. 85, 033501 (2014)

- (7) B. Tobias, et al., Rev. Sci. Instrum. 87, 11E103 (2016)

- (8) Y. Wang, et al., Nucl. Fusion **57**, 072007 (2017)

Figure 1 Receiver horn array assembly featuring integrated receiver chips and DIII-D optical arrangement